Variation-Aware Modeling, Design, and Optimization of Optical Interconnects

Optical interconnects are a promising substitute for electrical ones in data centers and high-performance computing systems. However, the highly dynamic traffic behavior of modern computational applications imposes design challenges in runtime-reconfigurability of optical interconnects, in addition to their inherent vulnerability to process variations. This project holistically explores modeling, design and optimization methodologies for optical interconnects that encompasses both variation awareness and runtime reconfigurability.

Modeling and Simulation

A comprehensive model library for silicon photonics optical devices is developed, including lasers and modulators of multiple kinds, multiplexers, demultiplexers, and high-speed photodetectors. Link-level simulation is enabled by integrating our SPICE-compatible models with electrical driving circuity in traditional electrical design automation (EDA) platforms, such as Cadence Virtuoso. The developed models are extensively validated by device- and circuit-level measurement data. Based on validated models and simulation methodologies, the impact of individual parameters on the overall performance of the optical link can be predicted.

Spatial Variation Characterization

Process variations of optical devices are learned from wafer-scale measurement data. Spatial variations of microring resonators are characterized into wafer-level, intra-die, and inter-die components. This hierarchical method can be used to generate trustworthy synthetic data with a remarkable resemblance to the measurement data, and thus facilitates the development and validation of novel variation alleviation techniques.

Variation Alleviation Techniques

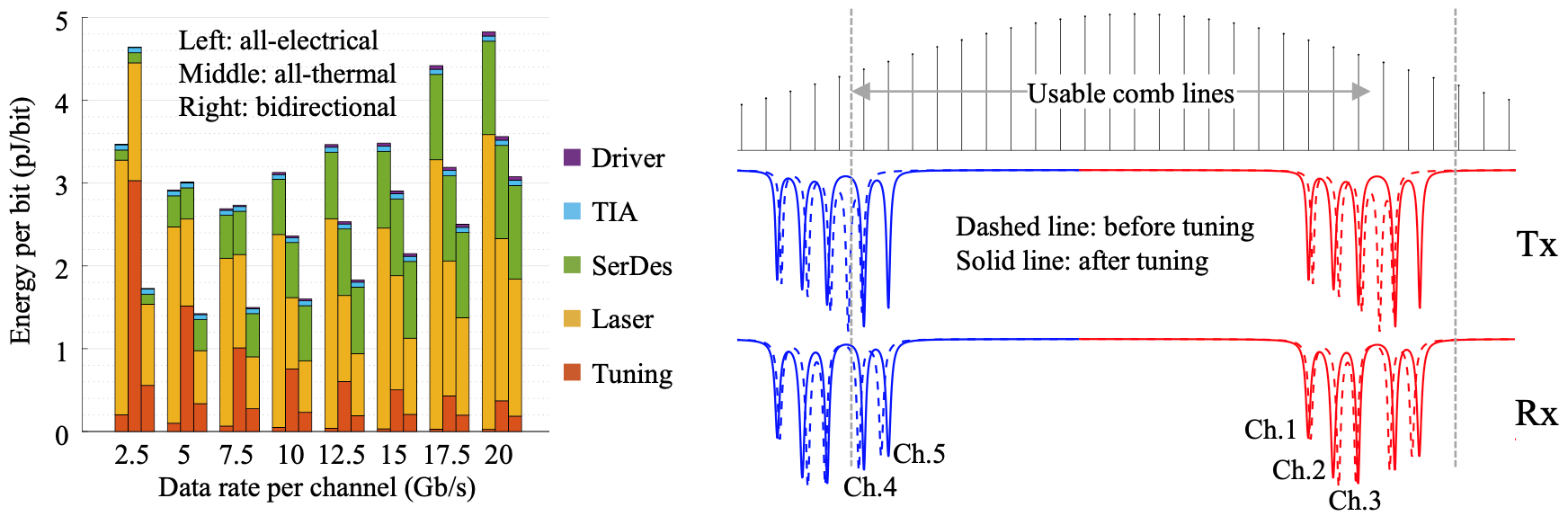

Efficient tuning techniques are vital to alleviate the energy overhead posed by variation calibration. Extensive studies are conducted on energy-efficient variation calibration techniques for optical interconnects including sub-channel redundant wavelengths, bidirectional tuning of microrings, and optimal pairing of transceivers. These techniques target orthogonal dimensions of the design space and thus can be applied simultaneously to achieve maximum energy saving.

Runtime Reconfiguration

Runtime reconfiguration is imperative to the energy efficiency of the optical interconnects by leveraging the highly dynamic traffic behavior without oversupplying bandwidth. Techniques such as adaptive tuning of the receiver sensitivity and dynamic laser power scaling (DLPS) are proposed to provide runtime traffic adaptability of the optical interconnects. We further propose to incorporate both network reconfiguration and traffic pattern adjustments to achieve better scalability to different kinds of traffic patterns. On average, a 66% reduction of the energy-latency product is achieved, compared to the baseline where the optimization techniques are not applied.

Publication:

Yuyang Wang, Jared Hulme, Peng Sun, Mudit Jain, M. Ashkan Seyedi, Marco Fiorentino, Raymond G. Beausoleil, and Kwang-Ting Cheng, “Characterization and Applications of Spatial Variation Models for Silicon Microring-Based Optical Transceivers,” in 57th Design Automation Conference (DAC), 2020.

Yuyang Wang and Kwang Ting Cheng, “Task Mapping-Assisted Laser Power Scaling for Optical Network-on-Chips,” in IEEE/ACM International Conference on Computer-Aided Design, (ICCAD), 2019.

Yuyang Wang, M. Ashkan Seyedi, Jared Hulme, Marco Fiorentino, Raymond G. Beausoleil, and Kwang-Ting Cheng, “Bidirectional Tuning of Microring-Based Silicon Photonic Transceivers for Optimal Energy Efficiency,” in 24th Asia and South Pacific Design Automation Conference (ASP-DAC), 2019.

Yuyang Wang, M. Ashkan Seyedi, Rui Wu, Jared Hulme, Marco Fiorentino, Raymond G. Beausoleil, and Kwang-Ting Cheng, “Energy-Efficient Channel Alignment of DWDM Silicon Photonic Transceivers,” in Design, Automation & Test in Europe Conference & Exhibition (DATE), 2018.

Rui Wu, M. Ashkan Seyedi, Yuyang Wang, Jared Hulme, Marco Fiorentino, Raymond G. Beausoleil, and Kwang-Ting Cheng, “Pairing of Microring-Based Silicon Photonic Transceivers for Tuning Power Optimization,” in 23rd Asia and South Pacific Design Automation Conference (ASP-DAC), 2018.

Zeyu Zhang, Rui Wu, Yuyang Wang, Chong Zhang, Eric J. Stanton, Clint L. Schow, Kwang-Ting Cheng, and John E. Bowers, “Compact Modeling for Silicon Photonic Heterogeneously Integrated Circuits,” Journal of Lightwave Technology, vol. 35, no. 14, pp. 2973–2980, Jul. 2017.

Rui Wu, Yuyang Wang, Zeyu Zhang, Chong Zhang, Clint L. Schow, John E. Bowers, and Kwang-Ting Cheng, “Compact Modeling and Cicuit-Level Simulation of Silicon Nanophotonic Interconnects,” inDesign, Automation & Test in Europe Conference & Exhibition (DATE), 2017.

Fan Lan, Rui Wu, Chong Zhang, Yun Pan, and Kwang-Ting Cheng, “DLPS: Dynamic Laser Power Scaling for Optical Network-on-Chip,” in 22nd Asia and South Pacific Design Automation Conference (ASP-DAC), 2017.

Rui Wu, Chin-Hui Chen, Tsung-Ching Huang, Ray Beausoleil, and Kwang-Ting Cheng, “Spatial Pattern Analysis of Process Variations in Silicon Microring Modulators,” in IEEE Optical Interconnects Conference (OI), 2016.

Rui Wu, Chin-hui Chen, M. Ashkan Seyedi, Tsung-Ching Huang, Marco Fiorentino, Ray Beausoleil, and Kwang-Ting Cheng, “Large-Signal Model for Small-Size High-Speed Carrier-Injection Silicon Microring Modulator,” in OSA Integrated Photonics Research, Silicon, and Nano-Photonics Conference (IPR), 2016.

Rui Wu, Chin-Hui Chen, Jean-Marc Fedeli, Maryse Fournier, Kwang-Ting Cheng, and Raymond G. Beausoleil, “Compact Models for Carrier-Injection Silicon Microring Modulators,” Optics Express, vol. 23, no. 12, p. 15545, Jun. 2015.

Rui Wu, Chin-Hui Chen, Cheng Li, Tsung-Ching Huang, Fan Lan, Chong Zhang, Yun Pan, John E. Bowers, Raymond G. Beausoleil, and Kwang-Ting Cheng, “Variation-Aware Adaptive Tuning for Nanophotonic Interconnects,” IEEE/ACM International Conference on Computer-Aided Design (ICCAD), 2015.

Yan Zheng, Peter Lisherness, Ming Gao, Jock Bovington, Kwang-Ting Cheng, Hong Wang, and Shiyuan Yang, “Power-Efficient Calibration and Reconfiguration for Optical Network-on-Chip,” Journal of Optical Communications and Networking, vol. 4, no. 12, p. 955, Dec. 2012.